Alongside some new bulletins for his or her 2nm course of node plans, TSMC has additionally launched a progress and roadmap replace for his or her N3 household course of applied sciences at right this moment’s 2023 North American Expertise Symposium. TSMC’s remaining era of FinFET-based course of nodes, the N3 household is anticipated to stay round in some form or type for a few years to come back because the densest node obtainable for purchasers who do not want a extra cutting-edge GAAFET-based course of.

TSMC’s massive roadmap updates on the N3 entrance have been with N3P and its excessive efficiency variant, N3X. As revealed right this moment by TSMC, N3P can be an optical shrink of N3E, providing enhanced efficiency, lowered energy consumption, and elevated transistor density in comparison with N3E, all whereas sustaining compatibility with N3E’s design guidelines. In the meantime, N3X will wed excessive efficiency with 3nm-class densities, providing increased clockspeeds for prime efficiency CPUs and different processors.

N3E: 3nm for Everybody Is on Schedule

As a fast refresher, TSMC’s N3 (3nm-class) household of course of applied sciences is comprised of a number of variants, together with baseline N3 (aka N3B), relaxed N3E with lowered prices, N3P with enhanced efficiency and chip density, and N3X with increased voltage tolerances. Final yr the corporate additionally talked about N3S with maximized transistor density, however this yr the corporate stays tight lipped about this node and it’s not talked about anyplace in its slides.

TSMC’s vanilla N3 node options as much as 25 EUV layers, with TSMC utilizing EUV double-patterning on a few of them to make for increased logic and SRAM transistor density than N5. EUV steps are costly normally, and EUV double patterning drives these prices up additional, which is why this fabrication course of is simply anticipated for use by a handful of consumers who should not as involved in regards to the excessive outlay required.

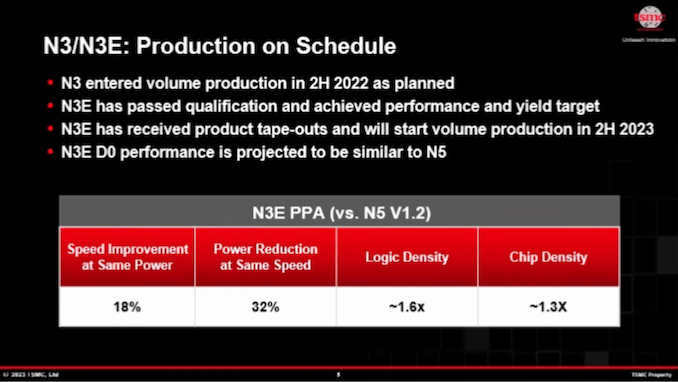

| Marketed PPA Enhancements of New Course of Applied sciences Information introduced throughout convention calls, occasions, press briefings and press releases |

|||

| TSMC | |||

| N3 vs N5 |

N3E vs N5 |

||

| Energy | -25-30% | -32% | |

| Efficiency | +10-15% | +18% | |

| Logic Space

Discount* % Logic Density* |

0.58x

-42% 1.7x |

0.625x

-37.5% 1.6x |

|

| SRAM Cell Measurement | 0.0199µm² (-5% vs N5) | 0.021µm² (similar as N5) | |

| Quantity Manufacturing |

Late 2022 | H2 2023 | |

Nearly all of TSMC’s purchasers enthusiastic about a 3nm-class course of are anticipated to make use of the relaxed N3E node, which in response to TSMC is on schedule and reaching their efficiency targets. N3E makes use of as much as 19 EUV layers and doesn’t depend on EUV double patterning in any respect, lowering its complexity and prices. The trade-off is that N3E presents decrease logic density than N3, and it has the identical SRAM cell measurement as TSMC’s N5 node, making it considerably much less engaging to these clients who’re driving for density/space positive factors. Total, N3E guarantees a wider course of window and higher yields, that are two essential metrics in chip fabrication.

“N3E can be higher than N3 when it comes to yield, course of complexity, which straight translating into [wider] course of window,” mentioned Kevin Zhang, Vice President of Enterprise Improvement at TSMC.

N3P: Greater Efficiency, Greater Transistor Density

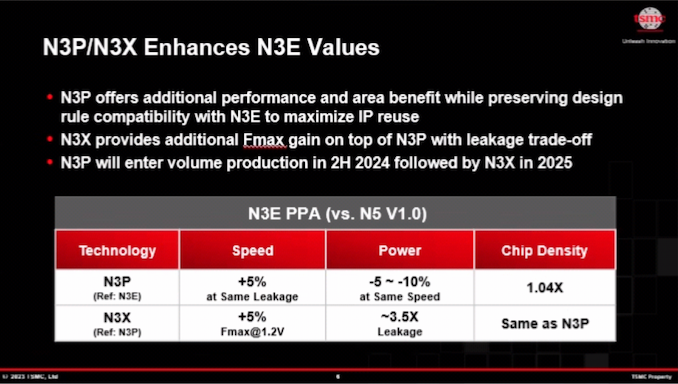

Following N3E, TSMC will proceed to optimize the N3 household’s transistor density with N3P, which is able to construct on N3E by providing improved transistor traits. The refined course of node will permit chip designers to both improve efficiency by 5% on the similar leakage or scale back energy by 5% ~ 10% on the similar clocks. The brand new node will even improve transistor density by 4% for a ‘blended’ chip design, which TSMC defines as a chip consisting of fifty% logic, 30% SRAM, and 20% analog circuits.

As a part of their dialogue on N3P, TSMC pressured that the density enchancment was achieved by adjusting the optical efficiency of its scanners. So it’s possible that TSMC will be capable to shrink all forms of chip buildings right here, which is able to make N3P a sexy node for SRAM-intensive designs.

“N3P is a efficiency increase, it has a 5% increased efficiency, a minimum of a 5% increased than N3E,” defined Zhang. It additionally has the two% optical shrink, which carry transistor density to 1.04x.”

| Marketed PPA Enhancements of New Course of Applied sciences Information introduced throughout convention calls, occasions, press briefings and press releases |

|||||

| TSMC | |||||

| N3 vs N5 |

N3E vs N5 |

N3P vs N4E |

N3X vs N3P |

||

| Energy | -25-30% | -32% | -5% ~ 10% | increased | |

| Efficiency | +10-15% | +18% | +5% | +5% Fmax @ 1.2V |

|

| Chip Density | ? | ? | |||

| SRAM Cell Measurement | 0.0199µm² (-5% vs N5) | 0.021µm² (similar as N5) | ? | ? | |

| Quantity Manufacturing |

Late 2022 | H2 2023 | H2 2024 | 2025 | |

Since N3P is an optical shrink of N3E, it would protect N3E’s design guidelines, enabling chip designers to shortly reuse N3E IP on the brand new node. Consequently, N3P can also be projected to be one in all TSMC’s hottest N3 nodes, so anticipate IP design homes like Cadence and Synopsys to supply quite a lot of IP for this course of know-how, reaping the advantages of ahead compatibility with current N3E within the course of. TSMC says that N3P can be manufacturing prepared within the second half of 2024.

N3X: Most Efficiency and Density

Lastly, for builders of high-performance computing functions like CPUs and GPUs, TSMC has for the previous few generations been providing its X household of excessive voltage, performance-focused nodes. As disclosed eventually yr’s occasion, the N3 household can be getting its personal X variant with the aptly named N3X node.

In comparison with N3E, N3X is projected to supply a minimum of 5% increased clockspeeds in comparison with N3P. That is being completed by making the node extra tolerant of upper voltages, permitting chip designers to crank up the clockspeeds in change for increased general leakage.

TSMC claims that N3X will assist voltages of (a minimum of) 1.2v, which is a reasonably excessive voltage for a 3nm-class fabrication course of. The leakage value, in flip, is important, with TSMC projecting a whopping 250% improve in energy leakage over the extra balanced N3P node. This underscores why N3X is de facto solely usable for HPC-class processors, and that chip designers might want to take further care to maintain their strongest (and power-hungry) chips in verify.

As for transistor density, N3X will supply the identical density as N3P. TSMC has not commented on whether or not it would additionally preserve design rule compatibility with N3P and N3E, so it will likely be fascinating to see what finally ends up occurring there.

The ultimate N3 household node in TSMC’s present roadmap, the corporate says that that N3X can be manufacturing prepared in 2025.

/cdn.vox-cdn.com/uploads/chorus_asset/file/25841912/Silo_Photo_021008.jpg)