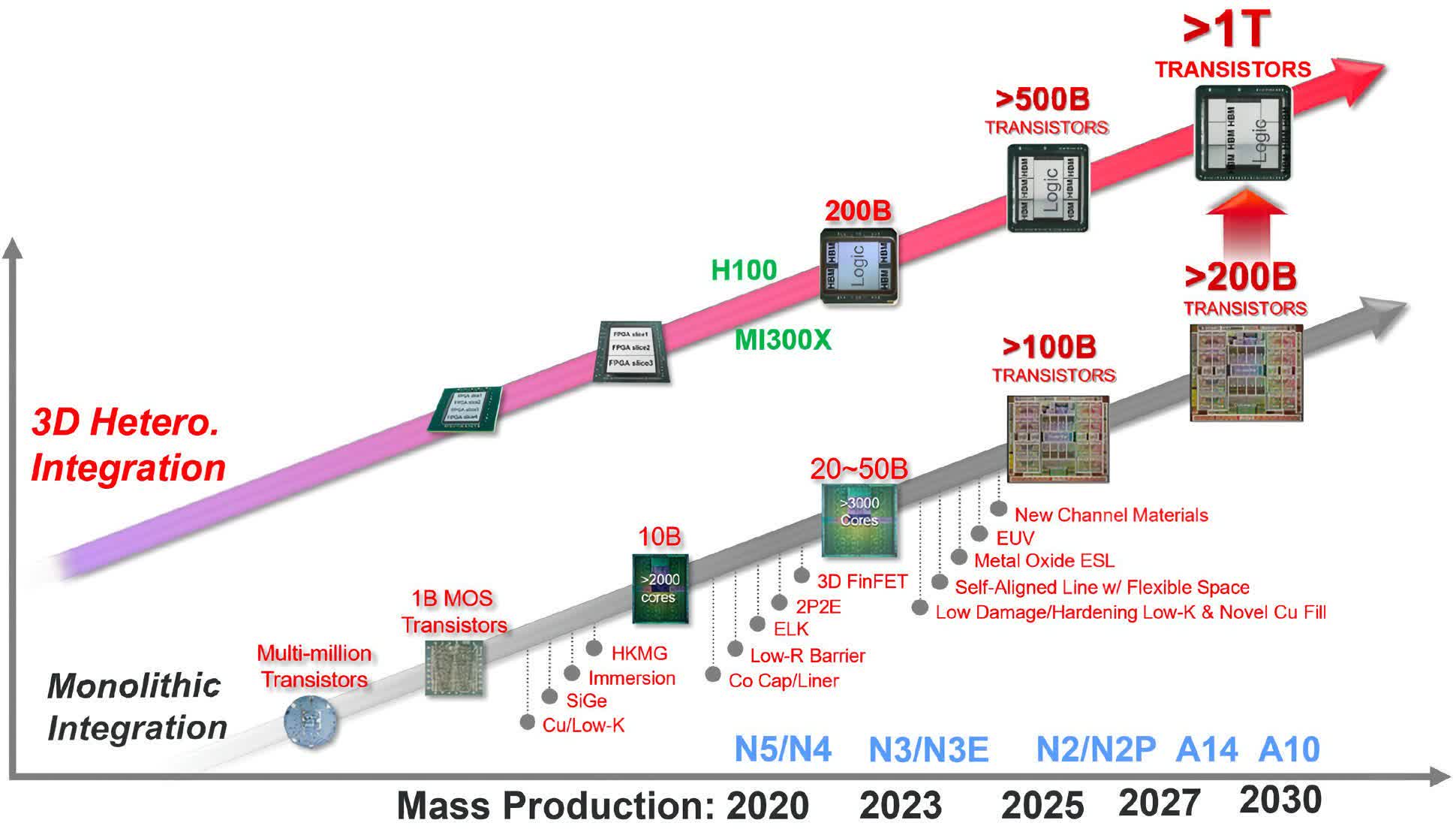

The large image: The worldwide firm confirmed the way it plans to proceed rising transistor density over the following a number of years. It additionally believes that the semiconductor business will transition to chiplet-based designs as properly.

On the current IEDM convention, TSMC unveiled a product roadmap for its semiconductors and next-generation manufacturing nodes that culminates in ultimately delivering a number of 3D-stacked collections of chiplet designs (3D Hetero Integration) with one trillion transistors on a single chip package deal. Developments in packaging applied sciences, equivalent to CoWoS, InFO and SoIC, will enable it to achieve that purpose and by 2030 it believes that its monolithic designs might attain 200 billion transistors.

Nvidia’s 80-billion-transistor GH100 is likely one of the most subtle monolithic processors at the moment in the marketplace. Nonetheless, as the dimensions of those processors continues to develop and change into extra pricey, TSMC believes that producers will undertake multi-chiplet architectures, equivalent to AMD’s recently-launched Intuition MI300X and Intel’s Ponte Vecchio, which has 100 billion transistors.

For now, TSMC will proceed to develop 2nm-class N2 and N2P manufacturing nodes and 1.4nm-class A14 and 1nm-class A10 fabrication processes. The corporate expects to start out 2nm manufacturing by the tip of 2025. In 2028, it should transfer onto a 1.4nm A14 course of, and by 2030, it expects to be producing 1nm transistors.

In the meantime, Intel is engaged on its 2nm course of (20A), and 1.8nm (18A), which it roughly expects to launch throughout the identical timeframe. One benefit of the brand new expertise is bottom energy supply, known as PowerVia, which ought to enable for larger logic densities, larger enhance clock speeds, and decrease energy leakage, leading to extra energy-efficient designs that would outperform TSMC’s choices.

Because the world’s largest foundry, TSMC is assured its course of nodes will outperform something from Intel. In an earnings name, TSMC CEO C.C. Wei stated that an inner evaluation confirmed the enhancements of the N3P expertise and that its 3nm-class manufacturing node demonstrated “comparable PPA” to Intel’s 18A node. He expects N3P to be even higher, boasting a extra aggressive “expertise maturity” and having vital value benefits.

Not one to disregard combating phrases, Intel CEO Pat Gelsinger claimed that its 18A course of node will outperform TSMC’s 2nm chips regardless of launching a yr earlier.

The market will quickly be capable to decide which is healthier. The Taiwan-based chip large expects to convey N3P into mass manufacturing within the second half of 2024 alongside its 20A and 18A merchandise.