In context: Nvidia CEO Jensen Huang has constantly proclaimed the demise of Moore’s Regulation in recent times. Though his counterparts at AMD and Intel maintain differing opinions, a latest presentation from Google seems to align with Huang’s perspective. This alignment may additionally assist elucidate TSMC’s developments over the previous a number of years.

The tech business continuously discusses how a lot time, if any, Moore’s Regulation has left. Google’s head of IC packaging, Milind Shah, just lately supported a previous assertion that the pattern, which has served as an important guidepost for the tech business, resulted in 2014.

In 1965, the late Intel co-founder Gordon Moore theorized that the variety of transistors per sq. inch on a circuit board would double about each two years. The idea, named after him, has largely held quick within the practically six a long time since however has just lately confronted turbulence.

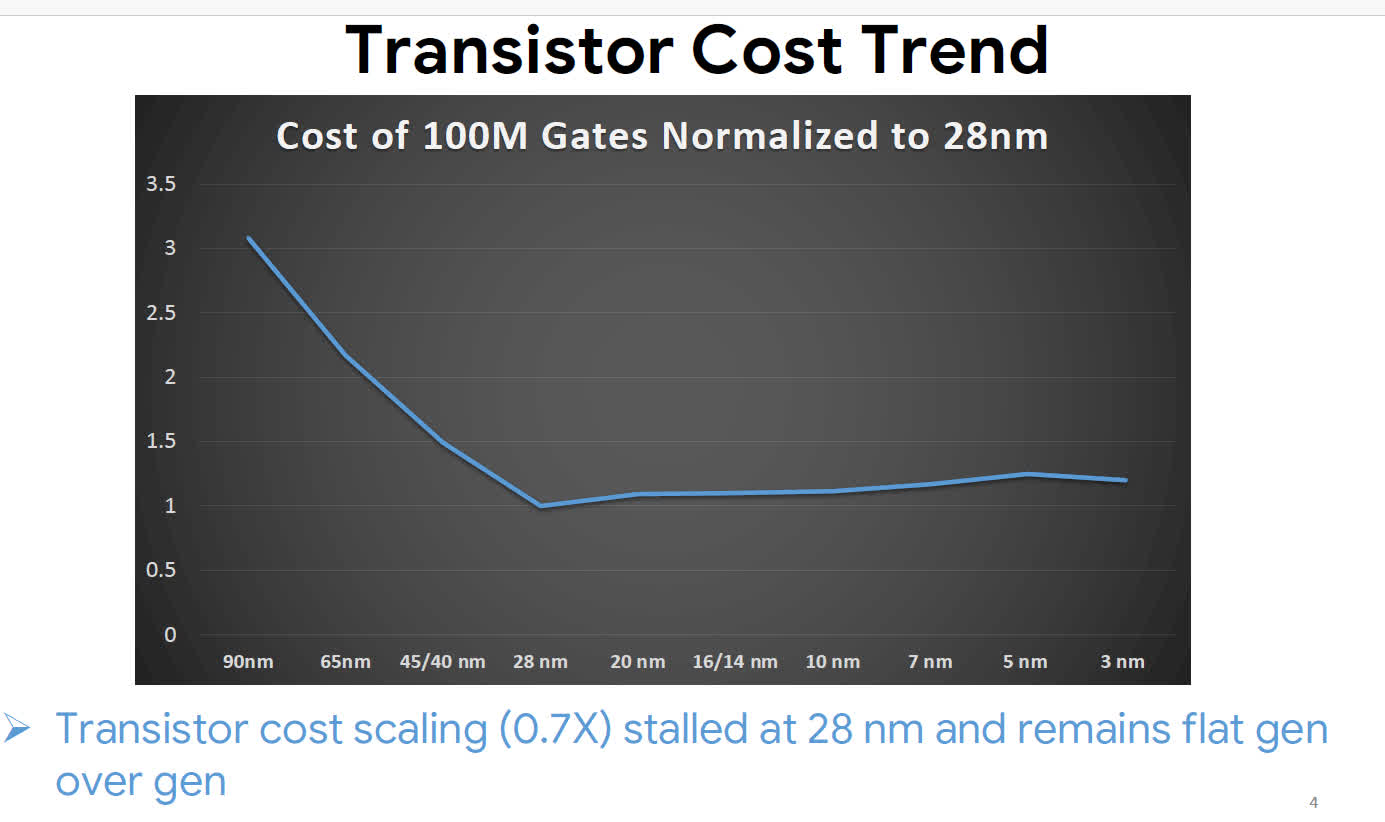

In 2014, MonolithIC CEO Zvi Or-Bach famous that the price of 100-million-gate transistors, which had beforehand been steadily falling, hit all-time low on the then-recent 28nm node. Semiconductor Digest experiences that Shah, talking on the 2023 IEDM convention, supported Or-Bach’s declare with a chart exhibiting that 100M gate costs have remained flat ever since, indicating that transistors have not gotten any cheaper within the final decade.

Though chipmakers proceed to shrink semiconductors and pack extra of them onto more and more highly effective chips, costs and energy consumption have elevated. Nvidia CEO Jensen Huang has tried to elucidate this pattern by proclaiming the demise of Moore’s Regulation a number of instances since 2017, stating that extra highly effective {hardware} will inevitably value extra and require extra vitality.

Some have just lately accused the Nvidia CEO of creating excuses for the rising costs of Nvidia graphics playing cards. In the meantime, the heads of AMD and Intel admit that Moore’s Regulation has at the very least slowed down however declare that they’ll nonetheless obtain significant efficiency and effectivity features from revolutionary methods like 3D packaging.

Nevertheless, the evaluation from Or-Bach and later Shah would possibly align with TSMC’s wafer value hikes, which sharply accelerated after 28nm in 2014. In line with DigiTimes, the Taiwanese large’s cost-per-wafer doubled over the following two years with the introduction of 10nm in 2016. The outlet estimated that the most recent 3nm wafers might value $20,000.

As TSMC and its rivals purpose towards 2nm and 1nm within the coming years, additional evaluation signifies that many of the semiconductor business’s latest progress comes from rising wafer costs. Regardless of wafer gross sales falling within the final couple of years, the typical value of TSMC’s wafers saved growing.