JEDEC on Tuesday printed the official specs for GDDR7 DRAM, the newest iteration of the long-standing reminiscence commonplace for graphics playing cards and different GPU-powered units. The latest technology of GDDR brings a mixture of reminiscence capability and reminiscence bandwidth features, with the later being pushed primarily by the swap to PAM3 signaling on the reminiscence bus. The most recent graphics RAM commonplace additionally boosts the variety of channels per DRAM chip, provides new interface coaching patterns, and brings in on-die ECC to keep up the efficient reliability of the reminiscence.

“JESD239 GDDR7 marks a considerable development in high-speed reminiscence design,” stated Mian Quddus, JEDEC Board of Administrators Chairman. “With the shift to PAM3 signaling, the reminiscence business has a brand new path to increase the efficiency of GDDR units and drive the continued evolution of graphics and numerous high-performance functions.”

GDDR7 has been in growth for a couple of years now, with JEDEC members making the primary disclosures across the reminiscence know-how a couple of 12 months in the past, when Cadence revealed the usage of PAM3 encoding as a part of their validation instruments. Since then we have heard from a number of reminiscence producers that we must always count on the ultimate model of the reminiscence to launch in 2024, with JEDEC’s announcement basically coming proper on schedule.

As beforehand revealed, the largest technical change with GDDR7 comes with the swap from two-bit non-return-to-zero (NRZ) encoding on the reminiscence bus to three-bit pulse amplitude modulating (PAM3) encoding. This variation permits GDDR7 to transmit 3 bits over two cycles, 50% extra information than GDDR6 working at an equivalent clockspeed. Because of this, GDDR7 can assist greater total information switch charges, the crucial part to creating every technology of GDDR successively quicker than its predecessor.

| GDDR Generations | |||||

| GDDR7 | GDDR6X (Non-JEDEC) |

GDDR6 | |||

| B/W Per Pin | 32 Gbps (Gen 1) 48 Gbps (Spec Max) |

24 Gbps (Transport) | 24 Gbps (Sampling) | ||

| Chip Density | 2 GB (16 Gb) | 2 GB (16 Gb) | 2 GB (16 Gb) | ||

| Complete B/W (256-bit bus) | 1024 GB/sec | 768 GB/sec | 768 GB/sec | ||

| DRAM Voltage | 1.2 V | 1.35 V | 1.35 V | ||

| Knowledge Fee | QDR | QDR | QDR | ||

| Signaling | PAM-3 | PAM-4 | NRZ (Binary) | ||

| Most Density | 64 Gb | 32 Gb | 32 Gb | ||

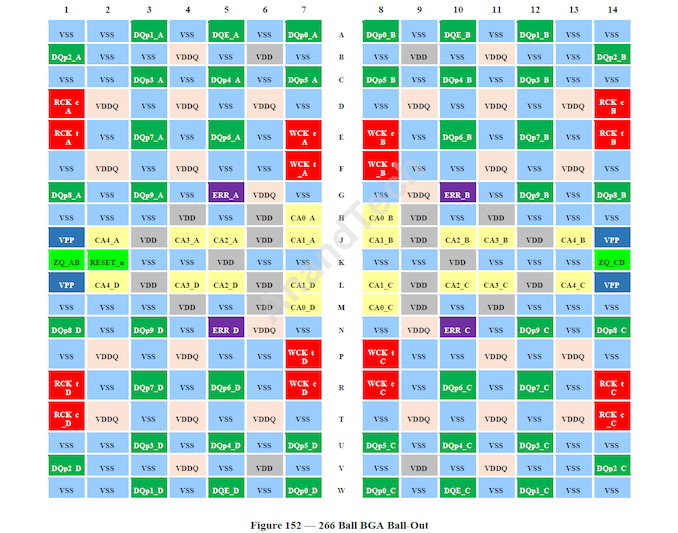

| Packaging | 266 FBGA | 180 FBGA | 180 FBGA | ||

The primary technology of GDDR7 is predicted to run at information charges round 32 Gbps per pin, and reminiscence producers have beforehand talked about charges as much as 36 Gbps/pin as being simply attainable. Nevertheless the GDDR7 commonplace itself leaves room for even greater information charges – as much as 48 Gbps/pin – with JEDEC going as far as touting GDDR7 reminiscence chips “reaching as much as 192 GB/s [32b @ 48Gbps] per machine” of their press launch. Notably, this can be a considerably greater enhance in bandwidth than what PAM3 signaling brings by itself, which suggests there are a number of ranges of enhancements inside GDDR7’s design.

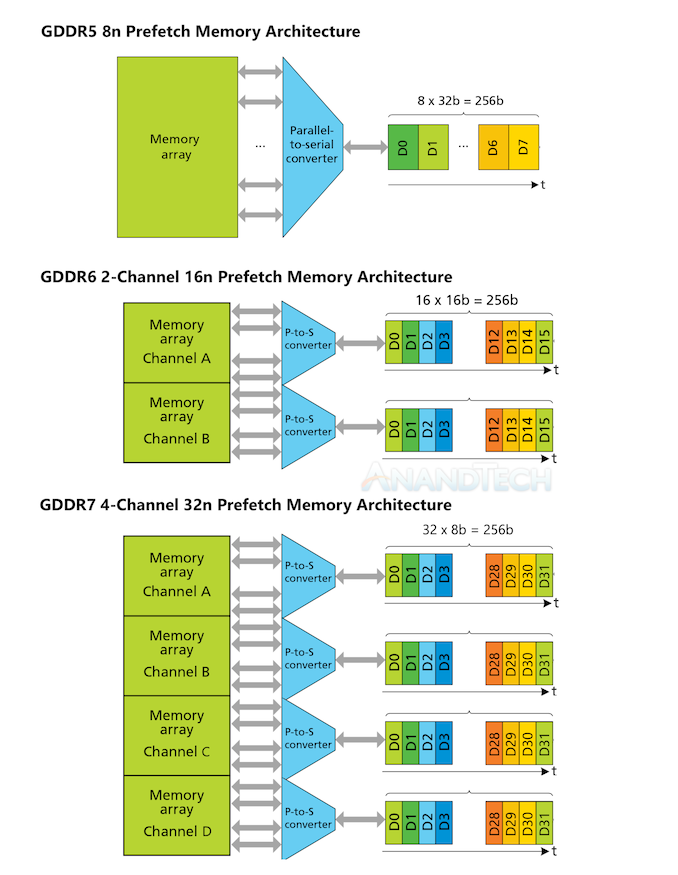

Digging deeper into the specification, JEDEC has additionally as soon as once more subdivided a single 32-bit GDDR reminiscence chip into a bigger variety of channels. Whereas GDDR6 supplied two 16-bit channels, GDDR7 expands this to 4 8-bit channels. The excellence is considerably arbitrary from an end-user’s viewpoint – it is nonetheless a 32-bit chip working at 32Gbps/pin regardless – however it has quite a lot of impression on how the chip works internally. Particularly as JEDEC has saved the 256-bit per channel prefetch of GDDR5 and GDDR6, making GDDR7 a 32n prefetch design.

GDDR Channel Structure. Authentic GDDR6-era Diagram Courtesy Micron

The online impression of all of that is that, by halving the channel width however preserving the prefetch dimension the identical, JEDEC has successfully doubled the quantity of information that’s prefetched per cycle of the DRAM cells. This can be a fairly commonplace trick to increase the bandwidth of DRAM reminiscence, and is actually the identical factor JEDEC did with GDDR6 in 2018. But it surely serves as a reminder that DRAM cells are nonetheless very sluggish (on the order of a whole bunch of MHz) and don’t get any quicker. So the one approach to feed quicker reminiscence buses is by fetching ever-larger quantities of information in a single go.

The change within the variety of channels per reminiscence chip additionally has a minor impression on how multi-channel “clamshell” mode works for greater capability reminiscence configurations. Whereas GDDR6 accessed a single reminiscence channel from every chip in a clamshell configuration, GDDR7 will entry two channels – what JEDEC is looking two-channel mode. Particularly, this mode reads channels A and C from every chip. It’s successfully equivalent to how clamshell mode behaved with GDDR6, and it signifies that whereas clamshell configurations stay supported on this newest technology of reminiscence, there aren’t some other tips being employed to enhance reminiscence capability past ever-increasing reminiscence chip densities.

On that notice, the GDDR7 commonplace formally provides assist for 64Gbit DRAM units, twice the 32Gbit max capability of GDDR6/GDDR6X. Non-power-of-two capacities proceed to be supported as properly, permitting for 24Gbit and 48Gbit chips. Help for bigger reminiscence chips additional pushes the utmost reminiscence capability of a theoretical high-end video card with a 384-bit reminiscence bus to as excessive as 192GB of reminiscence – a growth that might little doubt be welcomed by datacenter operators within the period of huge language AI fashions. With that stated, nonetheless, we’re nonetheless frequently seeing 16Gbit reminiscence chips used on as we speak’s reminiscence playing cards, despite the fact that GDDR6 helps 32Gbit chips. Coupled with the truth that Samsung and Micron have already disclosed that their first technology of GDDR7 chips will even prime out at 16Gbit/24Gbit respectively, it is secure to say that 64Gbit chips are fairly far off sooner or later proper now (so do not dump your 48GB playing cards fairly but).

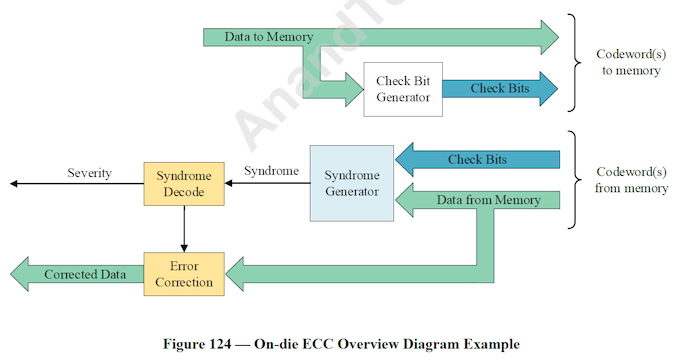

For his or her newest technology of reminiscence know-how, JEDEC can also be together with a number of new-to-GDDR reminiscence reliability options. Most notably, on-die ECC capabilities, just like what we noticed with the introduction of DDR5. And whereas we’ve not been in a position to get an official remark from JEDEC on why they’ve opted to incorporate ECC assist now, its inclusion isn’t a surprise given the reliability necessities for DDR5. In brief, as reminiscence chip densities have elevated, it has turn out to be more and more laborious to yield a “good” die with no flaws; so including on-chip ECC permits reminiscence producers to maintain their chips working reliably within the face of unavoidable errors.

This determine is reproduced, with permission, from JEDEC doc JESD239, determine 124

Internally, the GDDR7 spec requires a minimal of 16 bits of parity information per 256 bits of consumer information (6.25%), with JEDEC giving an instance implementation of a 9-bit single error correcting code (SEC) plus a 7-bit cyclic redundancy examine (CRC). General, GDDR7 on-die ECC ought to be capable of appropriate 100% of 1-bit errors, and detect 100% of 2-bit errors – falling to 99.3% within the uncommon case of 3-bit errors. Details about reminiscence errors can also be made accessible to the reminiscence controller, by way of what JEDEC phrases their on-die ECC transparency protocol. And whereas technically separate from ECC itself, GDDR7 additionally throws in one other reminiscence reliability function with command deal with parity with command blocking (CAPARBLK), which is meant to enhance the integrity of the command deal with bus.

In any other case, whereas the inclusion of on-die ECC is not more likely to have any extra of an impression on shopper video playing cards than its inclusion had for DDR5 reminiscence and shopper platforms there, it stays to be seen what this may imply for workstation and server video playing cards. The distributors there have used mushy ECC on prime of unprotected reminiscence for a number of generations now; presumably this may stay the case for GDDR7 playing cards as properly, however the common use of sentimental ECC makes issues much more versatile than within the CPU house.

This determine is reproduced, with permission, from JEDEC doc JESD239, determine 152

Lastly, GDDR7 can also be introducing a set of different reliability-related options, primarily associated to serving to PAM3 operation. This contains core impartial LFSR (linear-feedback shift register) coaching patterns with eye masking and error counters. LFSR coaching patterns are used to check and regulate the interface (to make sure effectivity), eye masking evaluates sign high quality, and error counters observe the variety of errors throughout coaching.

Technical issues apart, this week’s announcement contains statements of assist from the entire common gamers on either side of the isle, together with AMD and NVIDA, and the Micron/Samsung/SKhynix trifecta. It goes with out saying that every one events are eager to getting to make use of or promote GDDR7 respectively, given the reminiscence capability and bandwidth enhancements it’ll deliver – and particularly on this period the place something aimed on the AI market is promoting like hotcakes.

No particular merchandise are being introduced right now, however with Samsung and Micron having beforehand introduced their intentions to ship GDDR7 reminiscence this 12 months, we must always see new reminiscence (and new GPUs to pair it with) later this 12 months.

JEDEC requirements and publications are copyrighted by the JEDEC Strong State Know-how Affiliation. All rights reserved.